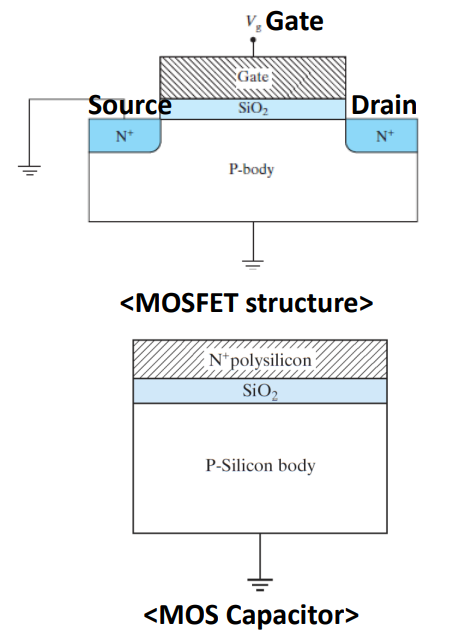

MOS는 metal-oxide-semiconductor의 약자이다.

커패시터는 반도체 바디(semiconductor body)라고도 하는 기판과

실리콘 산화막(SiO2)과 같은 절연막,

게이트(gate)라고 부르는 금속 단자로 구성된다.

얇은 산화막의 두께는 약 1.5nm 정도이다.

MOS 커패시터는 단일 소자 자체로 널리 쓰이지는 않고 MOS 트랜지스터의 일부를 형성하여

기능하게 되는데, MOS 트렌지스터는 현재까지 가장 널리 사용되는 반도체 소자이다.

MOS 트랜지스터는 양측에 PN 접합이 연결된 MOS 커패시터의 구조를 갖는다

평탄 밴드 조건과 평탄 밴드 전압

에너지 밴드 다이어그램을 그릴 때에는 실리콘 산화막을 중간에 두고 게이트와 바디를 각각

왼쪽과 오른쪽에 그리는 것이 일반적이다. 아래 그림과 같이 Vg=0 즉 아무런 전압도 가하지 않은 상태에서의

에너지 밴드 다이어 그램은 다소 복잡하다.

따라서 에너지 밴드 다이어그램을 그리는 법을 공부하기 전에 앞서 우선적으로 평탄 밴드 조건(flat-band condition) 이라는 특수한 전압 조건 하에서의 밴드 다이어 그램을 그리는 법을 알면 도움이 된다.

평탄 밴드 조건은 실리콘-실리콘 산화막 계면에서 실리콘 기판의 에너지 밴드(Ec 와 Ev)가 수평인 상태를 의미한다.

이러한 조건은 게이트에 음의 전압을 가하여 왼편의 밴드 다이어그램을 상승시킴으로서 형성할 수 있다.

(에너지 밴드 다이어그램은 전자 기준이므로 음의 전압을 가해줄 수록 에너지 밴드가 올라간다.)

에너지 밴드가 수평일 때에는 기판의 표면 전기장의 크기가 0이다.

따라서 산화막 내의 전기장의 크기도 0이다.

위와 같은 구조의 에너지 밴드 다이어그램을 만족시키기 위해 P형 실리콘 기판과 N+ 폴리실리콘 게이트 간에

인가되어야 하는 전압을 Vfb 를 평탄 밴드 전압(flat-band-voltage)라 하며 두 단자 간의 일함수의 차이로 정의된다.

여기서 일함수는 E0와 Ef 의 차이로 결정된다.

위의 경우에는 Vfb가 음의 값을 나타내며 그 값은 -0.7V 이다.

MOS Band Diagram Guildlines

MOS의 에너지 밴드 다이어그램을 분석하기 이전에 기억해야할 3가지 가정을 짚고 넘어가자

첫째 , semi conductor 내에는 전류가 발생하지 않는다.

-> 따라서 페르미 레벨 Ef가 flat 한 특성을 지닌다.

둘째, 산화막 (SiO2) 내에는 어떠한 charge도 존재하지 않는다고 가정한다.

셋째, 경계면에서 Oxide 밴드의 휘어진 정도가 경계면에서 Si 밴드의 휘어짐 정도의 약 3배이다.

위 식에서 보는 것 처럼 Vg 즉 게이트 전압은 평탄밴드 전압에 표면 전기장과 산화막에 걸리는 전압을

더한 것으로 구할 수 있다.

평탄 밴드 상태에서는 SiO2 와 Si 밴드가 휘어져 있지 않기 때문에 산화막에 걸리는 전압과

표면 전기장의 크기가 0이기 때문에 Vg=Vfb 라는 식을 도출할 수 있게된다.

P형 실리콘 기판과 N+ 폴리실리콘 게이트에서 평탄 밴드 조건 시

Vg=Vfb=-0.7V